Introduction

IC (Integrated Circuit) Design & Verification tools are specialized Electronic Design Automation (EDA) software used to design, simulate, validate, and verify semiconductor chips. These tools support workflows from RTL (Register Transfer Level) design to physical layout, ensuring chips function correctly before fabrication.

With the growing complexity of chips used in AI, automotive systems, consumer electronics, and high-performance computing, IC design tools have become mission-critical. Errors at the silicon stage are extremely costly, making robust verification and simulation essential in modern chip development.

Common real-world use cases:

- Digital and analog IC design

- RTL design and synthesis

- Functional and formal verification

- Timing and power analysis

- Physical design and layout

What buyers should evaluate:

- RTL design and synthesis capabilities

- Verification methodologies (UVM, formal verification)

- Simulation performance and accuracy

- Scalability for large chip designs

- Integration across design stages

- Support for advanced semiconductor nodes

- Automation and AI-assisted design

- Deployment flexibility (cloud vs on-premise)

- Debugging and visualization tools

Best for: Semiconductor companies, chip designers, VLSI engineers, ASIC/FPGA teams, and R&D organizations.

Not ideal for: General software developers, small teams without hardware focus, or users not involved in chip-level design.

Key Trends in IC Design & Verification Tools

- AI-driven chip design automation: Accelerating layout, synthesis, and verification workflows

- Shift-left verification: Early-stage validation to reduce costly errors

- Cloud-based EDA environments: Scalable compute for large simulations

- Hardware-software co-design: Integrated system-level modeling

- Advanced node support: Tools optimized for cutting-edge semiconductor processes

- Formal verification adoption: Increased use for ensuring correctness

- High-performance simulation: Leveraging parallel computing and HPC

- Reusable IP ecosystems: Faster design cycles using pre-built components

- Security-aware chip design: Addressing hardware-level vulnerabilities

- Automation of verification workflows: Reduced manual effort

How We Selected These Tools (Methodology)

- Industry adoption and leadership in semiconductor design

- Coverage across RTL, synthesis, simulation, and verification

- Performance in handling large-scale chip designs

- Integration with full EDA ecosystems

- Availability of advanced verification methodologies

- Vendor ecosystem strength and support

- Flexibility across deployment models

- Documentation, training, and community support

- Innovation in AI and automation

- Suitability across different enterprise scales

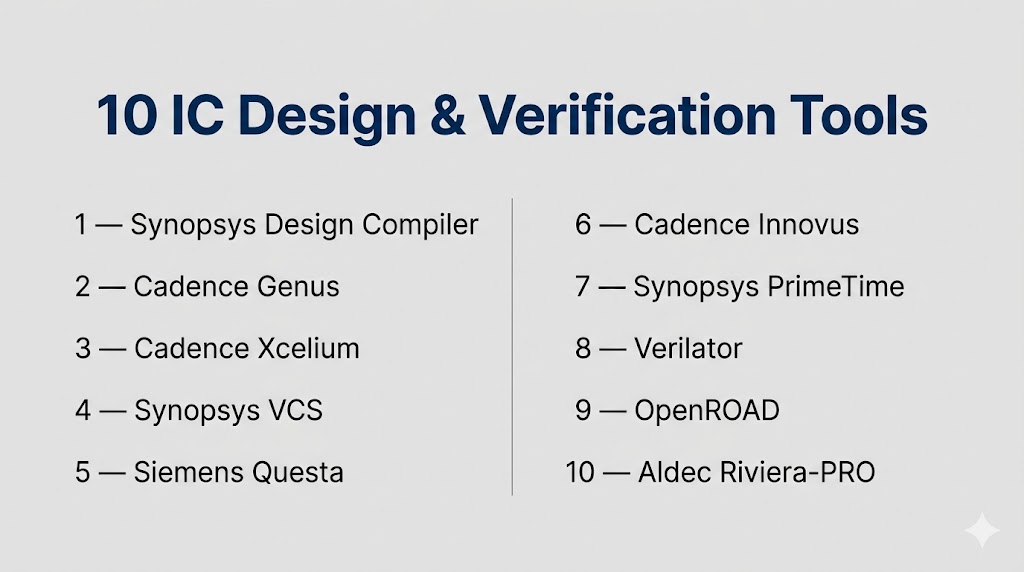

Top 10 IC Design & Verification Tools

#1 — Synopsys Design Compiler

Short description: A leading synthesis tool used for converting RTL designs into optimized gate-level implementations.

Key Features

- RTL synthesis

- Timing and power optimization

- Support for advanced nodes

- High scalability

- Integration with verification tools

- Constraint-driven optimization

Pros

- Industry standard

- High-performance synthesis

Cons

- Expensive

- Requires expertise

Platforms / Deployment

Linux

Self-hosted

Security & Compliance

Not publicly stated

Integrations & Ecosystem

Synopsys tools integrate across the full chip design lifecycle.

- Verification tools

- Physical design tools

- APIs

- Semiconductor workflows

Support & Community

Enterprise-level support with strong documentation.

#2 — Cadence Genus

Short description: A modern synthesis solution offering high performance and advanced optimization for digital IC design.

Key Features

- RTL synthesis

- Multi-threaded optimization

- Power-aware design

- Integration with physical design

- High scalability

Pros

- Efficient performance

- Strong Cadence ecosystem

Cons

- Complex setup

- High cost

Platforms / Deployment

Linux

Self-hosted

Security & Compliance

Not publicly stated

Integrations & Ecosystem

- Cadence ecosystem

- Verification tools

- APIs

- IC design workflows

Support & Community

Strong enterprise support.

#3 — Cadence Xcelium

Short description: High-performance simulation platform for digital and mixed-signal verification.

Key Features

- Fast simulation engine

- Mixed-signal simulation

- Debugging tools

- Scalable architecture

- UVM support

Pros

- High simulation speed

- Strong verification capabilities

Cons

- Expensive

- Learning curve

Platforms / Deployment

Linux

Self-hosted

Security & Compliance

Not publicly stated

Integrations & Ecosystem

- Cadence verification suite

- Debug tools

- APIs

- Simulation workflows

Support & Community

Enterprise-grade support.

#4 — Synopsys VCS

Short description: A widely used simulation tool for functional verification of digital designs.

Key Features

- High-speed simulation

- UVM support

- Debugging capabilities

- Coverage analysis

- Scalable performance

Pros

- Industry adoption

- Reliable performance

Cons

- Cost

- Complexity

Platforms / Deployment

Linux

Self-hosted

Security & Compliance

Not publicly stated

Integrations & Ecosystem

- Synopsys ecosystem

- Verification tools

- APIs

- Debug tools

Support & Community

Strong enterprise support.

#5 — Siemens Questa

Short description: A comprehensive verification platform for functional, formal, and simulation-based verification.

Key Features

- Functional verification

- Formal verification

- Simulation

- Coverage analysis

- Debugging tools

Pros

- Comprehensive verification

- Strong reliability

Cons

- Learning curve

- Licensing cost

Platforms / Deployment

Windows / Linux

Self-hosted

Security & Compliance

Not publicly stated

Integrations & Ecosystem

- Siemens EDA ecosystem

- Verification tools

- APIs

- Debug workflows

Support & Community

Strong enterprise support.

#6 — Cadence Innovus

Short description: A physical design platform for place-and-route and chip implementation.

Key Features

- Place-and-route

- Timing optimization

- Power optimization

- Advanced node support

- Physical verification

Pros

- High performance

- Scalable

Cons

- Complex

- Expensive

Platforms / Deployment

Linux

Self-hosted

Security & Compliance

Not publicly stated

Integrations & Ecosystem

- Cadence ecosystem

- Physical design tools

- APIs

- IC workflows

Support & Community

Enterprise-level support.

#7 — Synopsys PrimeTime

Short description: Industry-standard tool for static timing analysis and sign-off.

Key Features

- Static timing analysis

- Sign-off validation

- Power analysis

- High accuracy

- Integration with synthesis tools

Pros

- High accuracy

- Industry standard

Cons

- Expensive

- Specialized use

Platforms / Deployment

Linux

Self-hosted

Security & Compliance

Not publicly stated

Integrations & Ecosystem

- Synopsys ecosystem

- Design tools

- APIs

- IC workflows

Support & Community

Strong enterprise support.

#8 — Verilator

Short description: An open-source tool for fast simulation of digital designs.

Key Features

- High-speed simulation

- Open-source

- SystemVerilog support

- Integration with C++

- Lightweight

Pros

- Free

- Fast

Cons

- Limited features vs enterprise tools

- No full UVM support

Platforms / Deployment

Linux / macOS

Self-hosted

Security & Compliance

Not publicly stated

Integrations & Ecosystem

- Open-source ecosystem

- APIs

- Simulation tools

- Developer workflows

Support & Community

Active open-source community.

#9 — OpenROAD

Short description: Open-source tool for automated physical design of digital chips.

Key Features

- Automated place-and-route

- Open-source

- Scalable workflows

- Integration with open PDKs

- Chip design automation

Pros

- Free

- Growing ecosystem

Cons

- Still evolving

- Limited enterprise support

Platforms / Deployment

Linux

Self-hosted

Security & Compliance

Not publicly stated

Integrations & Ecosystem

- Open-source tools

- APIs

- Semiconductor workflows

- Research ecosystem

Support & Community

Academic and community-driven support.

#10 — Aldec Riviera-PRO

Short description: A simulation and verification platform for FPGA and ASIC designs.

Key Features

- HDL simulation

- Debugging tools

- Coverage analysis

- FPGA verification

- Mixed-language support

Pros

- Flexible

- Good FPGA support

Cons

- Smaller ecosystem

- Less adoption than top vendors

Platforms / Deployment

Windows / Linux

Self-hosted

Security & Compliance

Not publicly stated

Integrations & Ecosystem

- FPGA tools

- APIs

- Simulation workflows

- Debug tools

Support & Community

Moderate community and vendor support.

Comparison Table (Top 10)

| Tool Name | Best For | Platform(s) Supported | Deployment | Standout Feature | Public Rating |

|---|---|---|---|---|---|

| Synopsys Design Compiler | RTL synthesis | Linux | Self-hosted | Industry standard | N/A |

| Cadence Genus | Synthesis | Linux | Self-hosted | Optimization | N/A |

| Cadence Xcelium | Simulation | Linux | Self-hosted | High speed | N/A |

| Synopsys VCS | Verification | Linux | Self-hosted | UVM support | N/A |

| Siemens Questa | Verification | Windows, Linux | Self-hosted | Formal verification | N/A |

| Cadence Innovus | Physical design | Linux | Self-hosted | Place & route | N/A |

| Synopsys PrimeTime | Timing analysis | Linux | Self-hosted | Sign-off accuracy | N/A |

| Verilator | Open-source simulation | Linux, macOS | Self-hosted | Speed | N/A |

| OpenROAD | Open-source PnR | Linux | Self-hosted | Automation | N/A |

| Riviera-PRO | FPGA simulation | Windows, Linux | Self-hosted | Flexibility | N/A |

Evaluation & Scoring of IC Design & Verification Tools

| Tool Name | Core (25%) | Ease (15%) | Integrations (15%) | Security (10%) | Performance (10%) | Support (10%) | Value (15%) | Weighted Total |

|---|---|---|---|---|---|---|---|---|

| Synopsys DC | 10 | 5 | 9 | 7 | 10 | 9 | 5 | 8.10 |

| Cadence Genus | 9 | 6 | 9 | 7 | 9 | 9 | 6 | 8.00 |

| Xcelium | 9 | 6 | 9 | 7 | 10 | 9 | 6 | 8.15 |

| VCS | 9 | 6 | 9 | 7 | 10 | 9 | 6 | 8.15 |

| Questa | 9 | 6 | 9 | 7 | 9 | 9 | 6 | 8.00 |

| Innovus | 10 | 5 | 9 | 7 | 10 | 9 | 5 | 8.10 |

| PrimeTime | 10 | 5 | 9 | 7 | 10 | 9 | 5 | 8.10 |

| Verilator | 7 | 7 | 6 | 5 | 8 | 7 | 10 | 7.35 |

| OpenROAD | 7 | 6 | 6 | 5 | 7 | 6 | 10 | 7.00 |

| Riviera | 8 | 7 | 7 | 6 | 8 | 7 | 7 | 7.45 |

How to interpret scores:

- Enterprise tools dominate in performance and features

- Open-source tools provide high value but limited support

- Ease of use is generally lower across IC tools

- Scores are comparative, not absolute

- Choose based on workflow fit and scale

Which IC Design & Verification Tool Is Right for You?

Solo / Freelancer

- Best: Verilator, OpenROAD

SMB

- Best: Riviera-PRO

Mid-Market

- Best: Questa, Xcelium

Enterprise

- Best: Synopsys, Cadence tools

Budget vs Premium

- Budget: Verilator, OpenROAD

- Premium: Synopsys, Cadence

Feature Depth vs Ease of Use

- Deep: Synopsys, Cadence

- Easier: Riviera

Integrations & Scalability

- Best: Synopsys, Siemens

Security & Compliance Needs

- Enterprise tools recommended

Frequently Asked Questions (FAQs)

What are IC design tools?

They are software used to design and verify semiconductor chips.

Are these tools expensive?

Yes, enterprise tools are costly.

Can beginners use them?

They require strong technical knowledge.

What languages are used?

Verilog and VHDL are common.

Is simulation necessary?

Yes, it prevents costly errors.

What is verification?

Ensuring the chip behaves correctly.

Are open-source tools useful?

Yes, for learning and small projects.

Can I run them on cloud?

Some workflows support cloud deployment.

How long to learn?

Several months to years.

What industries use them?

Semiconductors, AI hardware, automotive.

Conclusion

IC Design & Verification tools are critical for building modern semiconductor devices. While enterprise tools like Synopsys and Cadence dominate the industry, open-source tools provide accessible entry points.